SHARC Fließkomma-DSP von Analog Devices

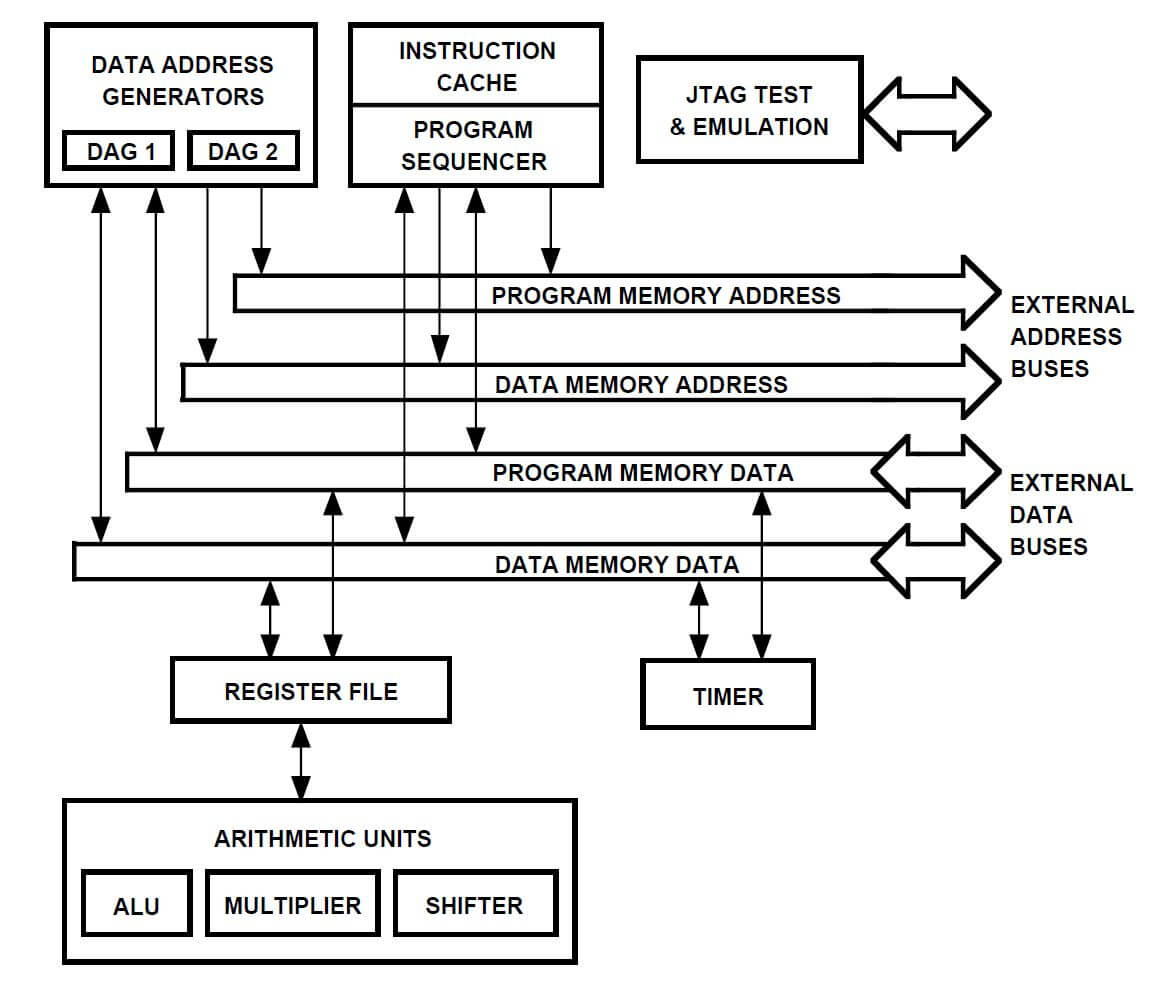

Analog Devices SHARC sind 32-Bit-Gleitkomma-DSP, die seit Anfang der 90er Jahre verfügbar und heute in der 6. Generation erhältlich sind. Ursprünglich handelte es sich bei SHARC (Super Harvard ARChitecture) um reine CPUs. Diese DSP zeichnen sich durch eine klare Struktur aus, haben einen nahezu uneingeschränkt orthogonalen Befehlssatz, d.h. (fast) jedes beliebige Register kann Quelle und Ziel einer Operation sein und die drei für DSP typischen Recheneinheiten Multiplier, ALU und Barrel-Shifter. In jedem Prozessortakt können je eine Multiplikation (zwei mit SIMD(), eine Addition (zwei mit SIMD), zwei Datenspeicherzugriffe (schreibend oder lesend), ein Programmspeicherzugriff und Pointer-Updates erfolgen.

Analog Devices SHARC sind 32-Bit-Gleitkomma-DSP, die seit Anfang der 90er Jahre verfügbar und heute in der 6. Generation erhältlich sind. Ursprünglich handelte es sich bei SHARC (Super Harvard ARChitecture) um reine CPUs. Diese DSP zeichnen sich durch eine klare Struktur aus, haben einen nahezu uneingeschränkt orthogonalen Befehlssatz, d.h. (fast) jedes beliebige Register kann Quelle und Ziel einer Operation sein und die drei für DSP typischen Recheneinheiten Multiplier, ALU und Barrel-Shifter. In jedem Prozessortakt können je eine Multiplikation (zwei mit SIMD(), eine Addition (zwei mit SIMD), zwei Datenspeicherzugriffe (schreibend oder lesend), ein Programmspeicherzugriff und Pointer-Updates erfolgen.

Eine typische Befehlszeile sieht beim SHARC wie folgt aus:

f8 = f0*f4, f12 = f8 + f12, f0 = dm(i0,m5), f4=pm(i8,m8);

Alle vier Instruktionen werden in einem Prozessortakt ausgeführt. Die Notation "fx" bezeichnet eines von 16 40-Bit-Registern, wenn sie für Fließkommaarithmetik (IEEE-754) benutzt werden. Die Notation "rx" bezeichnet dasselbe Register, wenn es für Festkommaarithmetik verwendet wird. Die ersten beiden Instruktionen, getrennt durch Kommas sind vermutlich selbsterklärend. Die dritte Instruktion lädt Register f0 mit dem Speicherinhalt (dm = Data Memory), der durch das Zeigerregister i0 adressiert wird. Das Register m5 wird benutzt, um i0 NACH dem Zugriff mit dem neuen Wert i0+m5 zu laden. Kleines Schmankerl: Wenn in der Klammer die beiden Operanden vertauscht werden, also dm(m5, i0), wird i0 VOR dem Zugriff mit dem neuen Wert i0+m5 geladen. Die vierte Instruktion ist entsprechend zu interpretieren, nur dass hier auf Daten im Programmspeicher zugegriffen wird (pm). Natürlich müssen alle verwendeten Register vor Ausführung dieser Befehlszeile mit sinnvollen Werten geladen worden sein, was bei allen Prozessoren jedoch selbstverständlich ist. Letztlich ist ein DSP nur ein CPU mit besonders für die digitale Signalverarbeitung geeigneten Sonderfunktionen. Der Barrel-Shifter kommt im Code-Beispiel übrigens nicht zum Einsatz. In Code-Beispielen für ein FFT kann man sehen, welche Möglichkeiten er bietet. Das im Jahr 1994 erschienene Applications Handbook erläutert im Detail, wie man Signalverarbeitungsfunktionen in Assembler implementiert.

Es soll hier nicht weiter im Detail auf die vielfältigen Möglichkeiten der Programmierung, speziell in Assembler eingegangen werden. Aber schon an diesem kleinen Beispiel, das dem Quellcode eines Digitalfilters entnommen wurde, wird klar, wir mächtig der SHARC-DSP im Vergleich zu einem handelsüblichen Mikrocontroller ist. Moderne ARM-Prozessoren enthalten inzwischen einige der für DSP typischen Eigenschaften, bei SHARC-Prozessoren findet man sie jedoch in ihrer reinsten Form. Weitergehende Literatur zum Thema SHARC findet man hier.

SHARC Generation 1

Die beiden Vertreter dieser ersten Generation waren der ADSP-21010 und der ADSP-21020. Diese beiden Prozessoren enthielten als einzige keinen internen Speicher, sondern separate Datenbusse für externen Daten- und Programmspeicher. Die Kernarchitektur dieser Ur-SHARCs blieb über die Generationen des SHARC praktisch unverändert und hat sich bis heute vor allem im Bereich Audiosignalverarbeitung zum Defakto-Standard entwickelt.

SHARC Generation 2

Die zweite Generation SHARC (ADSP-21060, ADSP-21061(L), ADSP-21062 und der low-cost ADSP-21065) wurden jeweils um internen dual-access Speicher und Schnittstellen (SPORT, LinkPort) erweitert. Mit Hilfe der bis zu sechs Linkports konnten zwei- und dreidimensionale Topologien (siehe Transputer!) realisiert werden. Die schnellsten Vertreter der zweiten Generation SHARC konnten mit 66 MHz getaktet werden und erzielten dabei dauerhaft bis zu 132 MFLOPs Rechenleistung.

SHARC Generation 3

SHARC-Prozessoren der dritten Generation (ADSP-21160, ADSP-21161) wurden durch ein SIMD-Rechenwerk (Single Instruction Multiple Data) erweitert und konnten besonders bei der Berechnung von FIR-Filtern und FFT bei gleichem Systemtakt erhebliche Geschwindigkeitsvorteile erzielen.

SHARC Generation 4

LinkPorts entfielen bei der vierten Generation SHARC (ADSP-2126x, ADSP-2136x) zugunsten eines flexibleren I/O-Konzepts, das die CPU dank zahlreicher DMA-Kanäle eheblich entlastet. Da sich SHARC-Prozessoren als ideal für Audio-Anwendungen erwiesen hatten, wurden u.a. S/PDIF-Schnittstellen und zahlreiche Audio-Algorithmen im ROM (z.B. AAC, Dolby Surround) angeboten. Taktraten bis zu 400MHz und bis zu 3 MBit on-chip RAM ermöglichen komplexe Algorithmen auch ohne externen Speicher.

SHARC Generation 5

SHARCs der fünften Generation (ADSP-214xx) enthalten bis zu 5 MBit on-chip RAM und können mit bis zu 450 MHz getaktet werden. Sie enthalten außerdem einen Koprozessor, der Filter (FIR oder IIR) oder FFTs unabhängig von der CPU berechnen können. Der Koprozessor wird zwar nur mit dem halben CPU-Takt betrieben, entlastet diese aber in bestimmten Anwendungen erheblich.

SHARC Generation 6

Die bisher letzte Generation von SHARC-Prozessoren wurde 2015 marktreif (ADSP-2156x, ADSP-2157x, ADSP-2158x, 1000MHz max.). Erstmals werden dual-core SHARCs angeboten, die über jeweils bis zu 5MBit eigenes RAM verfügen und auf Peripherie und externen Speicher über einen sog. System Crossbar zugreifen können. Erstmals werden auch SHARC-Prozessoren gemeinsam mit einem ARM Cortex-A5 auf einem Chip (ADSP-SC58x) angeboten. Der Cortex-A5 erweitert die Systemfähigkeiten durch PCIe (nur ADSP-SC589), USB, CAN und andere industriellen Schnittstellen. Ganz nebenbei erhielt der SHARC einen erweiterten Befehlssatz (64-bit SHARC+), der aber weitgehend rückwärts kompatibel zu den älteren Generationen ist. Mehr dazu in der SHARC+ Prozessor Übersicht.

Alle SHARC-Prozessoren mit Ausnahme der ersten Generation sind bis heute praktisch uneingeschränkt verfügbar, allerdings werden ältere Bauteile, z.B. der ADSP-21161, durch Preiserhöhungen zusehends unattraktiver für neue Designs.