Corelis JTAG/Boundary-Scan Webinare jetzt online

Das Testen von Baugruppen erfordert eine sauber geplante Strategie, besonders, wenn es um das Testen von Baugruppen mit hoher Dichte und Bauteilen mit Finepitch- oder BGA-Gehäusen geht.

Die jetzt online verfügbaren Webinare zum Thema 'Design for Test' zeigen wichtige Hinweise zur optimalen Gestaltung der Leiterplatte und der Testinfrastruktur auf. Alle Webinare sind in englischer Sprache verfügbar.

Webinar 1:

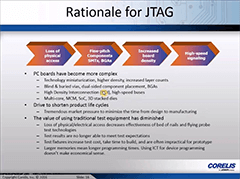

Warum Baugruppentests mit JTAG/Boundary-Scan sinnvoll sind

Tests mit JTAG/Boundary-Scan hat sich als die Methode zur Verbesserung der Testabdeckung bei gleichzeitiger Kostenreduktion und Zeitersparnis bewährt. Besonders spannend ist, dass die Testprozeduren schon während des Hardware-Designs entwickelt werden können um dann nahtlos in die Produktion einzufließen.

Tests mit JTAG/Boundary-Scan hat sich als die Methode zur Verbesserung der Testabdeckung bei gleichzeitiger Kostenreduktion und Zeitersparnis bewährt. Besonders spannend ist, dass die Testprozeduren schon während des Hardware-Designs entwickelt werden können um dann nahtlos in die Produktion einzufließen.

Dieses Webinar befasst sich mit den Vorteilen und Strategien zur optimalen Nutzung von JTAG/Boundary-Scan. Für den Abruf des Webinars klicken Sie bitte auf das Bild rechts.

Themen dieses Webinars sind:

- Wie können Tests auf Board- und Systemebene über den Produktlebenszyklus eingesetzt werden

- Wie kann JTAG/Boundary-Scan die Testabdeckung verbessern und gleichzeitig Zeit sparen

- Wie kann JTAG/Boundary-Scan in existierende Testsystemen (ICT) integriert werden

- Vorstellung von Corelis-Produkten und -dienstleistungen für Design for Test (DFT) und Testplanerstellung

Webinar 2:

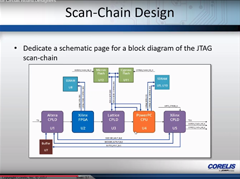

Richtlinien für Leiterplatten-Designer zur DFT-Optimierung

Wäre es nicht schön, wenn ein Leiterplatten-Design auf Anhieb liefe? Time-to-Market und natürlich auch Kosten erfordern ein möglichst fehlerfreies Ergebnis im ersten Anlauf. Dazu ist es nötig, Fehler früh zu erkennen und zu beheben. Ein gutes Design nach den hier aufgezeigten Regeln ist die Grundvoraussetzung für optimale Testbarkeit. Für den Abruf des Webinars klicken Sie bitte auf das Bild rechts.

Wäre es nicht schön, wenn ein Leiterplatten-Design auf Anhieb liefe? Time-to-Market und natürlich auch Kosten erfordern ein möglichst fehlerfreies Ergebnis im ersten Anlauf. Dazu ist es nötig, Fehler früh zu erkennen und zu beheben. Ein gutes Design nach den hier aufgezeigten Regeln ist die Grundvoraussetzung für optimale Testbarkeit. Für den Abruf des Webinars klicken Sie bitte auf das Bild rechts.

Themen dieses einstündigen Webinars sind:

- Grundlagen von Baugruppentests mit JTAG-Boundary-Scan

- Leiterplatten-Design mit zuverlässigen, high-speed JTAG-Scan-Ketten

- Einbindung von Komponenten ohne JTAG-Interface in Baugruppentests

- Typische Fehler und Workarounds